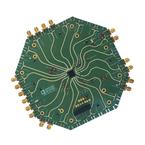

The EK1HMC7044LP10B from Analog Devices is a HMC7044 evaluation kit. The EV3HMC7044LP10B evaluation board is a compact, easy to use platform for evaluating all the features of the HMC7044 dual loop clock jitter cleaner. The HMC7044 meets the requirements of multicarrier GSM and LTE base station designs and offers a wide range of clock management and distribution features to simplify baseband and radio card clock tree designs. The high performance dual-loop core of the HMC7044 enables the base station designer to attenuate the incoming jitter of a primary system reference clock, such as a CPRI source with the help of the narrow-band configured first PLL loop which disciplines an external VCXO and to generate the low phase noise, high frequency clocks with the wider-band second PLL to drive data converter sample clock inputs. A 122.88MHz VCXO is mounted on the evaluation board to provide a complete solution. All inputs and outputs are configured as differential on evaluation board.

● Simple power connection using USB connection and on-board LDO voltage regulators

● LDOs can be bypassed for power measurements

● AC-coupled differential SMA connectors

● SMA connectors for 2 reference inputs, 6 clock outputs, 1 VCXO output

● Microsoft Windows based evaluation software with simple graphical user interface

● On-board PLL loop filter

● Easy access to digital input/output and diagnostic signals via input/output header (4 GPIOs)

● Status LEDs for diagnostic signals

● USB computer interface