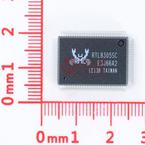

General Description

●The RTL8305SC is a 5-port Fast Ethernet switch controller that integrates memory, five MACs, and five physical layer transceivers for 10Base-T and 100Base-TX operation into a single chip. All ports support 100Base-FX, which shares pins (TX+-/RX+-) with UTP ports and needs no SD+/- pins, a development using Realtek proprietary technology. To compensate for the lack of auto-negotiation in 100Base-FX applications, the RTL8305SC can be forced into 100Base-FX half or full duplex mode, and can enable or disable flow control in fiber mode.

●Features

●■ 5-port integrated switch controller with memory and transceiver for 10Base-T and 100Base-TX with:

● ♦ 5-port 10/100M UTP or

● ♦ 4-port 10/100M UTP + 1-port MII/SNI or

● ♦ 4-port 10/100M UTP + 1-port MAC MII/SNI + 1-port PHY MII

●■ Supports the fifth port MAC circuit as PHY mode MII, SNI for router applications, and MAC mode MII for HomePNA or VDSL solutions

●■ Supports the fifth port PHY circuit as PHY mode MII for router and Gateway applications

●■ All ports support 100Base-FX with optional flow control enable/disable and full/half-duplex setting

●■ Supports FEFI function for fiber application

●■ Non-blocking wire-speed reception and transmission and non-head-of-line blocking forwarding

●■ Fully compliant with IEEE 802.3/802.3u auto-negotiation function

●■ Built-in high-efficiency SRAM for packet buffer, with 1K-entry lookup table and 16-entry CAM

●■ Supports broadcast storm filtering function

●■ Flow control fully supported:

● ♦ Half duplex: back pressure flow control

● ♦ Full duplex: IEEE 802.3x flow control

●■ Supports SMI (Serial Management Interface: MDC/MDIO) for programming and diagnostics

●■ Supports loop detection function with one LED to indicate the existence of a loop

●■ Supports MAC and PHY loopback function for diagnosis

●■ Supports up to 16 VLAN groups

●■ Flexible 802.1Q port/tag-based VLAN

●■ ARP VLAN for broadcast packets

●■ Leaky VLAN for unicast packets

●■ VLAN tag Insert/Remove function

●■ Supports QoS function on each port:

● ♦ QoS based on: (1) Port-based, (2) VLAN tag, (3) TCP/IP header’s TOS/DS

● ♦ Supports two-level priority queues

● ♦ Weighted round robin service

●■ Robust baseline wander correction for improved 100Base-TX performance

●■ Optional MDI/MDIX auto crossover for plug-and-play

●■ Physical layer port Polarity Detection and Correction function

●■ Optional EEPROM interface for configuration

●■ 25MHz crystal or 3.3V OSC input

●■ Single 3.3V power input can be transformed to 1.8V via a low-cost external BJT transistor

●■ Low power, 1.8/3.3V, 0.18µm CMOS technology, 128-pin PQFP package

●■ Supports special VLAN tag insert or remove function on per-port basis (egress) to separate WAN traffic from LAN traffic

●■ Optional 1536 or 1552 byte maximum packet length

●■ Supports reserved control frames (DID=0180C2000003~0180C200000F) filtering function

●■ Flexible LED indicators for link, activity, speed, full/half duplex, and collision

●■ LEDs blink upon reset for LED diagnostics

●■ Supports two power reduction methods:

● ♦ Power saving mode by cable detection

● ♦ Power down mode (via PHY register 0.11)

●■ Robust baseline wander correction for improved 100Base-TX performance

●■ Optional MDI/MDIX auto crossover for plug-and-play

●■ Physical layer port Polarity Detection and Correction function

●■ Optional EEPROM interface for configuration

●■ 25MHz crystal or 3.3V OSC input

●■ Single 3.3V power input can be transformed to 1.8V via a low-cost external BJT transistor

●■ Low power, 1.8/3.3V, 0.18µm CMOS technology, 128-pin PQFP package