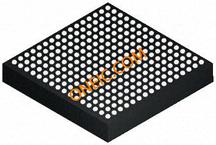

The EP3C5F256C8N is a Cyclone® III FPGA consists of 5136 vertically arranged logic elements (LEs), 414kb of embedded memory and 23 18x18 embedded multipliers. The architecture includes highly efficient interconnect and low-skew clock networks, providing connectivity between logic structures for clock and data signals. The logic and routing core fabric is surrounded by I/O elements (IOEs) and phase-locked loops (PLLs). The low-power Cyclone® III FPGA family is the third generation in the Altera® Cyclone FPGA series. With its unprecedented combination of low power, high functionality, the Cyclone III FPGA family broadens the number of high-volume, cost-sensitive applications that can benefit from an FPGA. The Cyclone III LS variant extends the family with higher density, higher memory, smaller packages and security features to protect your intellectual property (IP).

● 2 Phase-locked loops

● 70 Differential channels

● Hot-socketing operation support

● Routing architecture optimized for design separation flow with the Quartus® II software

● Ability to disable external JTAG port

● Error detection (ED) cycle indicator to core

● Internal oscillator enables system monitor and health check capabilities

● High memory-to-logic and multiplier-to-logic ratio

● High I/O count, low-and mid-range density devices for user I/O constrained applications

● Remote system upgrade without the aid of an external controller

● Dedicated cyclical redundancy code checker circuitry to detect single-event upset (SEU) issues