Part Datasheet Search > Microcontrollers > Freescale > MCF5206EAB40 Datasheet PDF

MCF5206EAB40 Datasheet PDF - Freescale

| Manufacturer: | Freescale |

| Category: | Microcontrollers |

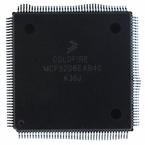

| Case Package: | QFP-160 |

| Description: | MPU ColdFire MCF5xxx Processor RISC 32Bit 0.35um 40MHz 3.3V 160Pin PQFP Tray |

| Documentation: | MCF5206EAB40 Datasheet (12 Pages) |

| Pictures: |

MCF5206EAB40 Datasheet PDF

ADatasheet has not yet included the datasheet for MCF5206EAB40

If necessary, please send a supplementary document request to the administrator

MCF5206EAB40 Datasheet PDF (12 Pages)

MCF5206EAB40 Specifications

| TYPE | DESCRIPTION |

|---|---|

| Mounting Style | Surface Mount |

| Frequency | 40 MHz |

| Number of Pins | 160 Pin |

| Supply Voltage (DC) | 3.30 V, 3.60 V (max) |

| Case/Package | QFP-160 |

| Halogen Free Status | Not Halogen Free |

| Clock Speed | 40.0 MHz |

| RAM Memory Size | 8K x 8 |

| Number of Bits | 32 Bit |

| Number of I/O Pins | 8 IO |

| Core Architecture | Coldfire |

| Operating Temperature (Max) | 70 ℃ |

| Operating Temperature (Min) | 0 ℃ |

MCF5206EAB40 Size & Package

| TYPE | DESCRIPTION |

|---|---|

| Product Lifecycle Status | Not Recommended for New Designs |

| Packaging | Tray |

| Operating Temperature | 0℃ ~ 70℃ |

MCF5206EAB40 Environmental

MCF5206EAB40 Function Overview

The MCF5206e integrated microprocessor combines a ColdFire® core with several peripheral

●functions such as a DRAM controller, timers, parallel and serial interfaces, and system integration. This device is an enhanced version of the MCF5206, which is in production today. Not only does the MCF5206e provide a performance upgrade to the MCF5206 due to the increased 4-Kbyte I-cache, 8-Kbyte SRAM and increased frequency, but this device also integrates an additional multiply accumulate (MAC) unit, hardware divide, and two-channel DMA to the device while maintaining pin compatibility with the MCF5206.

●Features List

●The following are the primary features of the MCF5206e integrated processor:

●• ColdFire Version 2 core

●— Variable-length RISC

●— 32-bit internal address bus with 28-bit external bus; chip select and DRAM decoding use

●internal 32 bit

●— 32-bit data base

●— 16 user-visible 32-bit wide registers

●— Supervisor and user modes for system protection

●— Vector base register to relocate exception-vector table

●— Optimized for high level language constructs

●— 50 MIPS at 54 MHz

●• Multiply accumulate

●— High speed, complex arithmetic functions for signal processing applications

●— Single clock issue rate with 3-stage execution pipeline

●— One MAC cycle for 16x16 and 32x32 multiplies, all with 32-bit accumulate

●— Four-Kbyte direct-mapped instruction cache

●— Eight-Kbyte on-chip SRAM that provides one-cycle access to critical code and data

●• DRAM controller

●— Programmable refresh timer provides CAS before RAS refresh

●— Support for 2 separate memory banks

●— Support for fast page mode DRAMs and extended-data-out (EDO) DRAMs

●— External bus master access

●• DMA controller

●— Two fully programmable channels with external request pins supporting dual-address and

●single address transfers with 32-bit capability

●— Two address pointers per channel that can increment or remain constant

●— 16-bit transfer counter per channel

●— Operand packing and unpacking

●— Auto-alignment transfers for efficient block movement

●— Bursting and cycle stealing

●— Two clock-cycle internal access

●• Two universal synchronous/asynchronous receiver/transmitters (UARTs)

●— Full duplex operation

●— Baud-rate generator

●— Modem control signals (CTS, RTS)

●— Processor-interrupt capability

●• Dual 16-bit general-purpose multimode timers

●— 8-bit prescaler

●— Timer input and output pins

●— 12 ns resolution with 54 MHz system clock

●— Processor interrupt capability

●• Motorola bus (M-Bus) module

●— Interchip bus interface for EEPROMs, LCD controllers, A/D converters, keypads

●— Compatible with industry-standard I2C bus

●— Master or slave modes supporting multiple masters

●— Automatic interrupt generation with programmable level

●• System interface

●— Glueless bus interface to 8 bit, 16 bit, and 32 bit DRAM, SRAM, ROM, and I/O devices

●— Eight programmable chip selects and programmable wait states and port sizes allowing

●external bus masters to access chip selects

●— Programmable external interrupts

●— 8-bit general-purpose I/O interface

●— System protection

●– 16-bit software watchdog timer with prescaler

●– Double bus fault monitor

●– Bus timeout monitor

●– Spurious interrupt monitor

●– Programmable interrupt controller (low interrupt latency, 3 external interrupt inputs, and

●programmable interrupt priority and autovector generator)

●— IEEE 1149.1 test (JTAG) support

●• System debug interface

●— Real-time trace

●— Background debug mode (BDM)

●• Fully static 3.3-volt operation with 5-volt tolerant inputs

●• 160-pin QFP package; pin-compatible with MCF5206

show more

MCF5206EAB40 Documents

MCF5206 Documents

Freescale

NXP

MPU ColdFire MCF5xxx Processor RISC 32Bit 0.35um 40MHz 3.3V 160Pin PQFP Tray

NXP

NXP MCF5206EAB54 Microprocessor, ColdFire V2 MCF520X Series, 54MHz, 32Bit, 512Byte, 4.75V to 5.25V, QFP-160

NXP

NXP MCF5206ECAB40 Microprocessor, ColdFire V2 MCF520X Series, 40MHz, 32Bit, 512Byte, 4.75V to 5.25V, QFP-160

Freescale

MPU ColdFire MCF5xxx Processor RISC 32Bit 0.35um 40MHz 3.3V 160Pin PQFP Tray

Freescale

MPU ColdFire MCF5xxx Processor RISC 32Bit 0.35um 40MHz 3.3V 160Pin PQFP Tray

Freescale

MPU ColdFire MCF5xxx Processor RISC 32Bit 0.35um 54MHz 3.3V 160Pin PQFP Tray

NXP

MPU ColdFire MCF5xxx Processor RISC 32Bit 0.35um 40MHz 3.3V 160Pin PQFP

Part Datasheet PDF Search

Example: STM32F103

72,405,303 Parts Datasheet PDF, Update more than 5,000 PDF files ervery day.